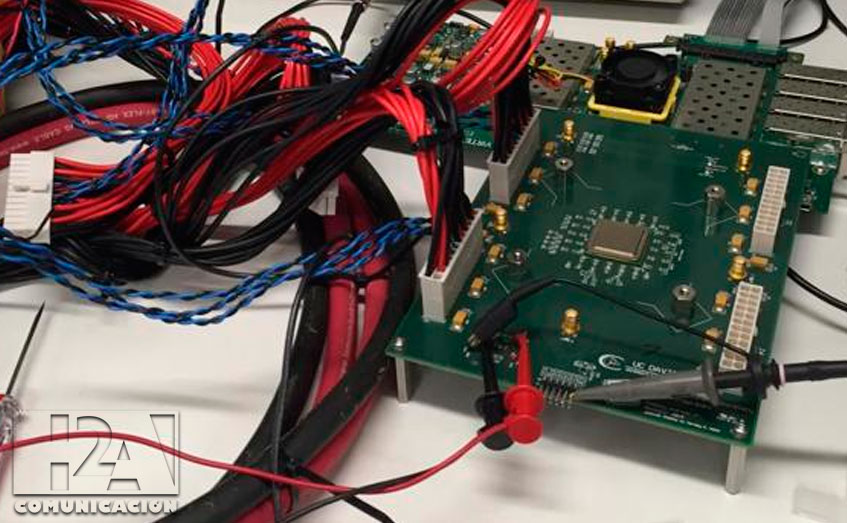

Bautizado como «KiloCore», es capaz de ejecutar más de 1.78 billones de instrucciones por segundo y contiene 621 millones de transistores, según sus desarrolladores, pertenecientes a la Universidad de California en Davis

El avance en nanotecnología es profundo y el reto de alcanzar mayores cotas de energía supera con creces algunos fundamentos teóricos del pasado. Los procesadores con varios núcleos -bloques que se encargan de ejecutar las instrucciones- han venido popularizándose en aras de la obtención de un mayor rendimiento e independiencia de las tareas. Rizando más el rizo, un grupo de ingenieros de la Universidad de California en Davis ha logrado el desarrollo del primer microchip que contiene mil núcleos o procesadores programables e inpendientes.

Lo han bautizado como «KiloCore» y, según los responsables de este proyecto presentado en el Simposio de Tecnología VLSI en Honolulu recientemente, es capaz de ejecutar más de 1.78 billones de instrucciones por segundo y contiene 621 millones de transistores. Fabricado por IBM utilizando su propia tecnología CMOS de 32 nanómetros -que utiliza en sus desarrollos más avanzados-, puede considerarse el más rápido y potente.

Cada uno de esos núcleos (o «cores», en la denominación anglosajona) puede ejecutar su propio programa independientemente de los otros, funcionando a una frecuencia de 1.78 Ghz, logrando una transferencia de datos entre ellos en lugar de utilizar la memoria caché. El chip «KiloCore» es capaz de procesar 115.000 millones de instrucciones por segundo únicamente con solo 0.7 vatios, energía que podría suministrar una simple pila AA, un tamaño de pila estándar utilizado por multitud de aparatos electrónicos.

La premisa del procesamiento en paralelo, ya que cada microprocesador ofrece una velocidad independiente, se puede apagarse de forma automática de cara a ahorrar más energía cuando no se necesita. Es decir, optimizar recursos. «KiloCore» ejecuta cien instrucciones más y de manera más eficiente que un procesador de ordenador portátil actual. Hasta ahora, los diseños de procesadores más grandes no han superado los 300 núcleos en un mismo chip.

«La idea es romper una aplicación en muchos pedazos pequeños, cada uno de los cuales se pueden ejecutar en paralelo en diferentes procesadores»Bevan Bass

«Es el procesador de múltiples núcleos más eficiente jamás registrado en una universidad», asegura Bevan Baas, profesor de ingeniería e informática de la universidad y el director del equipo diseñador de la arquitectura de este chip, aunque destaca que pese en principio está destinado para fines de investigación y por el momento se descarta su venta comercial.

«La idea es romper una aplicación en muchos pedazos pequeños, cada uno de los cuales se pueden ejecutar en paralelo en diferentes procesadores, lo que permite un alto rendimiento con menor consumo de energía», explica este experto. A juicio de los responsables del proyecto, se trata de «un enfoque más flexible» que la llamada técnica SIMD (Single Instruction, Multiple Data, en español: «una instrucción, múltiples datos»), utilizada normalmente por los procesadores convencionales.

fuente:abc.es